Rangkaian Sekuensial

Oleh = Mochammad Haldi Widianto

Pengertian Rangkaian Logika Sekuensial

Rangkaian logika sekuensial adalah rangkaian digital yang output-nya bergantung tidak hanya pada keadaan input saat ini, tetapi juga pada keadaan output sebelumnya. Dengan kata lain, rangkaian ini memiliki memori yang memungkinkan menyimpan informasi keadaan sebelumnya.

Rangkaian logika sekuensial digunakan secara luas dalam sistem digital seperti register, counter, memori, dan pengendali logika.

Latch dan Flip-Flop

Latch

- Latch adalah rangkaian dasar penyimpan data yang bersifat asinkron, artinya outputnya berubah segera saat input berubah tanpa memerlukan sinyal clock.

- Latch biasanya memiliki sinyal enable (aktif tinggi atau aktif rendah) yang mengontrol kapan data disimpan atau dilepaskan.

- Contoh latch yang umum: SR Latch.

Flip-Flop

- Flip-flop adalah rangkaian penyimpan data yang bekerja secara sinkron, artinya output hanya berubah pada saat terjadi transisi sinyal clock tertentu (rising edge atau falling edge).

- Flip-flop merupakan pengembangan dari latch dengan tambahan sinyal clock.

- Flip-flop banyak digunakan dalam desain rangkaian digital karena kontrol timing yang lebih baik.

Jenis-Jenis Flip-Flop

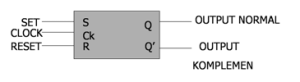

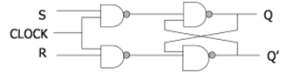

1. Flip-Flop RS (Set-Reset) Berdetak (Clocked RS Flip-Flop)

Gambar 1. Tabel Kebenaran FF-RS

Flip-flop RS adalah flip-flop dasar yang memiliki dua input utama: S (Set) dan R (Reset), serta input clock.

- Flip-flop ini bekerja secara sinkron dan aktif saat clock bernilai HIGH (aktif HIGH).

- Kondisi input S=R=1 tidak diperbolehkan karena menyebabkan keadaan tidak stabil (race condition).

Tabel Kebenaran Flip-Flop RS Berdetak

| Clock | S | R | Q(t+1) (Output berikutnya) | Keterangan |

| 1 | 0 | 0 | Q(t) (tetap) | Tidak berubah |

| 1 | 0 | 1 | 0 | Reset |

| 1 | 1 | 0 | 1 | Set |

| 1 | 1 | 1 | Tidak valid | Kondisi tidak diperbolehkan |

Simbol Flip-Flop RS

text

_______

S —-| |

| RS |—- Q

R —-| Flip- |

Clk –| Flop |—- Q’

———

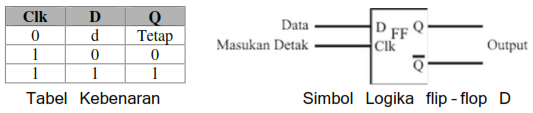

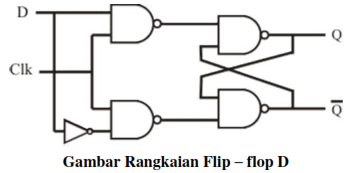

2. Flip-Flop D (Data atau Delay Flip-Flop)

Flip-flop D memiliki satu input data (D) dan satu input clock (Clk). Output Q mengikuti nilai input D pada saat terjadi transisi clock positif (rising edge).

- Jika clock tidak berubah, output Q tetap menyimpan nilai sebelumnya (memori).

Tabel Kebenaran Flip-Flop D

| Clock (rising edge) | D | Q(t+1) (Output berikutnya) | Keterangan |

| 1 | 0 | 0 | Output mengikuti D |

| 1 | 1 | 1 | Output mengikuti D |

| 0 | X | Q(t) (tetap) | Tidak terjadi perubahan |

Simbol Flip-Flop D

text

_______

D —-| |

| D |—- Q

Clk –| Flip- |

| Flop |—- Q’

———

3. Flip-Flop JK

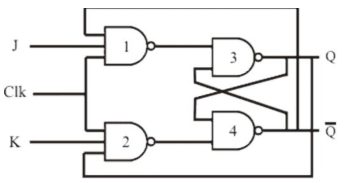

Gambar 2. JK-FlipFlop

Flip-flop JK adalah pengembangan dari flip-flop RS yang menghilangkan kondisi tidak valid (S=R=1). Flip-flop JK memiliki dua input: J dan K, serta input clock.

- Jika J=K=0, output tetap (memori).

- Jika J=1 dan K=0, output diset ke 1.

- Jika J=0 dan K=1, output di-reset ke 0.

- Jika J=K=1, output toggle (berubah ke kebalikan nilai sebelumnya).

Flip-flop JK sering digunakan sebagai pencacah (counter) dan pembagi frekuensi.

Tabel Kebenaran Flip-Flop JK

| Clock (rising edge) | J | K | Q(t+1) (Output berikutnya) | Keterangan |

| 1 | 0 | 0 | Q(t) (tetap) | Tidak berubah |

| 1 | 0 | 1 | 0 | Reset |

| 1 | 1 | 0 | 1 | Set |

| 1 | 1 | 1 | Q'(t) (toggle) | Berubah kebalikan |

Simbol Flip-Flop JK

text

_______

J —-| |

| JK |—- Q

K —-| Flip- |

Clk –| Flop |—- Q’

———

Penjelasan Transisi Clock

- Transisi Positif (Rising Edge): Clock berubah dari 0 ke 1. Flip-flop merespon perubahan input pada saat ini.

- Transisi Negatif (Falling Edge): Clock berubah dari 1 ke 0. Flip-flop merespon perubahan input pada saat ini.

Flip-flop dapat dirancang untuk aktif pada salah satu jenis transisi ini, tergantung kebutuhan aplikasi.

Aplikasi Flip-Flop

- Register: Menyimpan data sementara dalam komputer.

- Counter: Menghitung pulsa clock untuk berbagai aplikasi seperti jam digital.

- Pembagi Frekuensi: Mengurangi frekuensi sinyal clock.

- Pengendali State Machine: Mengatur urutan operasi dalam sistem digital.

Kesimpulan

Flip-flop dan latch adalah blok dasar dalam rangkaian logika sekuensial yang memungkinkan penyimpanan data dan pengendalian timing sinyal digital. Memahami karakteristik dan fungsi masing-masing jenis flip-flop sangat penting dalam desain sistem digital modern.

Referensi:

http://matkul.xyz/memahami-rangkaian-sekuensial-dan-macam-macam-flip-flop/

http://matkul.xyz/memahami-rangkaian-sekuensial-dan-macam-macam-flip-flop/

Comments :